## DESIGN AND ANALYSIS OF HYBRID BRIDGE MULTILEVEL INVERTER FOR SYMMETRICAL AND ASYMMETRICAL SOURCES

Sushil Kumar<sup>1</sup>, Vinay Pathak<sup>2</sup>

<sup>1</sup>M. Tech Scholar, BIT, Bhopal (M.P.), India.

<sup>2</sup>Assistant Professor BIT, Bhopal (M.P.), India.

Corresponding author mail- Sk23021998@gmail.com

### ABSTRACT

This work presents the design and analysis of a Hybrid Bridge Multilevel Inverter (HBMI) topology for both symmetrical and asymmetrical sources. Multilevel inverters (MLIs) have gained significant attention due to their ability to produce high-quality output waveforms with reduced harmonic distortion and lower electromagnetic interference. The proposed HBMI topology leverages the advantages of traditional H-bridge inverters while integrating auxiliary circuits to enhance performance and efficiency of the conventional bridge converter. In the symmetrical configuration, identical DC voltage sources are utilized, facilitating a straightforward design and control strategy. For the asymmetrical configuration, different DC voltage levels are employed, offering a higher number of output voltage levels with the same number of power electronic components, thereby improving the output waveform quality without significantly increasing the circuit complexity. The proposed converter uses two auxiliary circuits, each auxiliary consisting of a four diodes along with the one IGBT with the bridge inverter. The seven level voltages are achieved using HBMI and the proposed topology is applicable for both symmetrical and asymmetrical sources. The study includes a detailed analysis of the device count and harmonic investigation of voltage & current at load side.

**Keywords:** HBMLI (Hybrid Bridge Multilevel inverter); Harmonics (THD); Symmetrical Source; Asymmetrical source; Switches.

### 1. INTRODUCTION

The need for high-efficiency power conversion systems has been accentuated by the global push towards sustainable energy solutions and the electrification of transportation. Conventional two-level inverters, while effective in basic power conversion tasks, often fall short in applications requiring high power quality[1]. The primary limitations of two-level inverters include significant harmonic distortion in the output waveform, high voltage stress across the switching devices, and substantial electromagnetic interference, which can adversely affect the performance and lifespan of connected equipment [2]. Multilevel inverters address these challenges by producing output waveforms that closely approximate a sine wave, thereby reducing harmonic distortion and electromagnetic interference. The concept of multilevel inverters was introduced to achieve higher power ratings and improve the quality of the output voltage and current [3]. By synthesizing a staircase waveform from several voltage levels, MLIs can significantly reduce the total harmonic distortion (THD) in the output, thereby enhancing the efficiency and reliability of the power conversion process.

Multilevel inverters (MLIs) have emerged as a transformative technology in the field of power electronics, owing to their superior performance in generating high-quality output waveforms with minimal harmonic distortion and reduced electromagnetic interference [4].

The evolution of MLIs has been driven by the increasing demand for efficient and reliable power conversion in various applications, including renewable energy systems, electric vehicles, and industrial motor drives. Among the various MLI topologies, the Hybrid Bridge Multilevel Inverter (HBMI) stands out for its ability to integrate the advantages of traditional H-bridge inverters with advanced auxiliary circuits, thereby enhancing the overall performance and efficiency of the power conversion process.

### 2. HYBRID BRIDGE MULTILEVEL INVERTER

The Hybrid Bridge Multilevel Inverter (HBMI) topology represents a significant advancement over traditional MLI designs by integrating auxiliary circuits with conventional H-bridge inverters. This integration not only enhances the performance and efficiency of the inverter but also provides greater flexibility in accommodating both symmetrical and asymmetrical sources [5,6].

The proposed HBMI topology leverages the benefits of H-bridge inverters, such as modularity and simplicity, while incorporating auxiliary circuits to achieve higher voltage levels and improved output waveform quality [7, 8].

- **Symmetrical Configuration**

In the symmetrical configuration of the HBMI, identical DC voltage sources are used for all inverter cells. This approach simplifies the design and control strategy, as the voltage levels generated by each cell are equal. The primary advantage of the symmetrical configuration is the ease of implementation and control, making it suitable for applications where uniform voltage levels are available.

- **Asymmetrical Configuration**

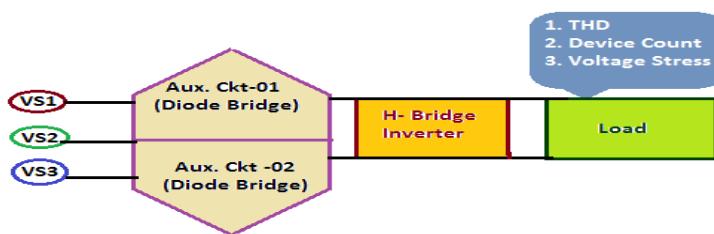

The asymmetrical configuration of the HBMI employs different DC voltage levels for the inverter cells, resulting in a higher number of output voltage levels with the same number of power electronic components. This configuration improves the output waveform quality by reducing the THD, without significantly increasing the circuit complexity. The asymmetrical configuration is particularly advantageous in applications where multiple voltage levels can be easily obtained, such as in renewable energy systems with varying input sources [9, 10]. Figure 2.1 shows the block diagram of proposed HBMI inverter.

**Figure-2.1: Block diagram of HBMI**

### 3. SIMULATION OF HYBRID BRIDGE MULTILEVEL INVERTER

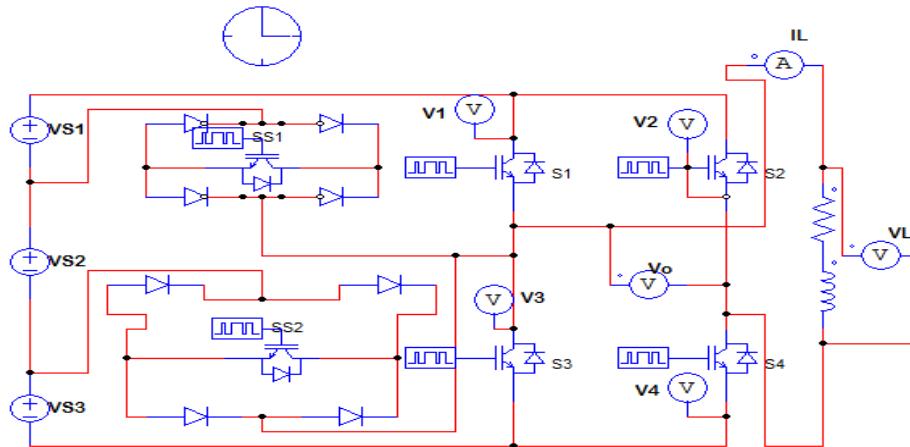

The Hybrid Bridge Multilevel Inverter (HBMI) topology has gained traction in recent years due to its ability to generate high-quality output waveforms with minimal harmonic distortion and enhanced efficiency. By integrating auxiliary circuits with conventional H-bridge inverters, the HBMI topology can accommodate both symmetrical and asymmetrical sources, making it versatile for various high-power applications [11, 12]. This paper presents a comprehensive simulation of the HBMI topology using PSIM software, a powerful tool for designing and analyzing power electronics systems. The simulations cover both symmetrical and asymmetrical configurations, highlighting the performance, efficiency, and harmonic characteristics of the inverter. Figure 3.1 presents the simulation of HBMI in PISIM software.

- **Simulation Setup in PSIM-** PSIM software is widely used for simulating power electronics systems due to its user-friendly interface and robust simulation capabilities. The simulation setup for the HBMI topology involves designing the inverter circuit, setting up the control strategy, and analyzing the performance under different source configurations.

- **Circuit Design-** The circuit design in PSIM involves creating the H-bridge inverter cells and integrating the auxiliary circuits. Each H-bridge cell consists of four IGBTs configured to generate three voltage levels (positive, negative, and zero). The auxiliary circuits, composed of diodes and additional IGBTs, are connected to the H-bridge cells to achieve the desired seven-level output.

For the symmetrical configuration, identical DC voltage sources are connected to each H-bridge cell. In the asymmetrical configuration, different DC voltage sources are used, typically in a binary sequence to maximize the number of output levels.

**Table 3.1** Simulation Parameters

| S.No. | Components Description    | Symmetrical HBMI         | Asymmetrical HBMI        |

|-------|---------------------------|--------------------------|--------------------------|

| 1.    | Voltage Source - $V_{S1}$ | 100V                     | 100V                     |

| 2.    | Voltage Source - $V_{S2}$ | 100V                     | 200V                     |

| 3.    | Voltage Source - $V_{S3}$ | 100V                     | 300V                     |

| 4.    | Load                      | $R=10$ ohms, $L=0.001$ H | $R=10$ ohms, $L=0.001$ H |

| 5.    | Switching frequency       | 5KHZ                     | 5KHZ                     |

| 6.    | Diodes                    | Ideal                    | Ideal                    |

| 7.    | IGBT                      | Ideal                    | Ideal                    |

Figure 3.1: Simulation of HBMI in PISIM

#### 4. SIMULATION RESULTS

The simulation results for both symmetrical and asymmetrical configurations provide insights into the performance, efficiency, and harmonic characteristics of the HBMI topology.

##### Load Voltage and Current

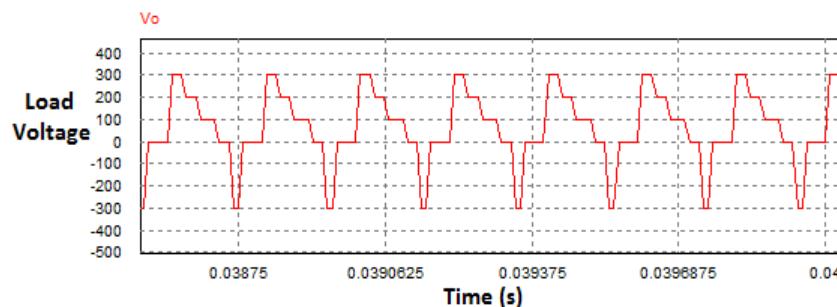

- **Symmetrical Configuration**

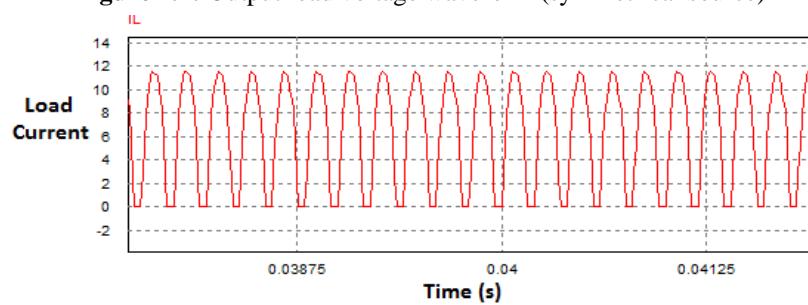

In the symmetrical configuration, the HBMI produces a seven-level output voltage waveform. The simulation results show that the output waveform closely approximates a sinusoidal waveform, with significantly reduced THD compared to a conventional two-level inverter. The harmonic analysis indicates that most of the higher-order harmonics are effectively eliminated, resulting in a clean output waveform. The voltage level are  $\pm 100$ ,  $\pm 200$  and  $\pm 300$  while the magnitude of current is observed as 11.8 A as shown in figure 4.1 and 4.2 respectively.

Figure 4.1: Output load voltage waveform (symmetrical source)

Figure 4.2: Output load current waveform (asymmetrical source)

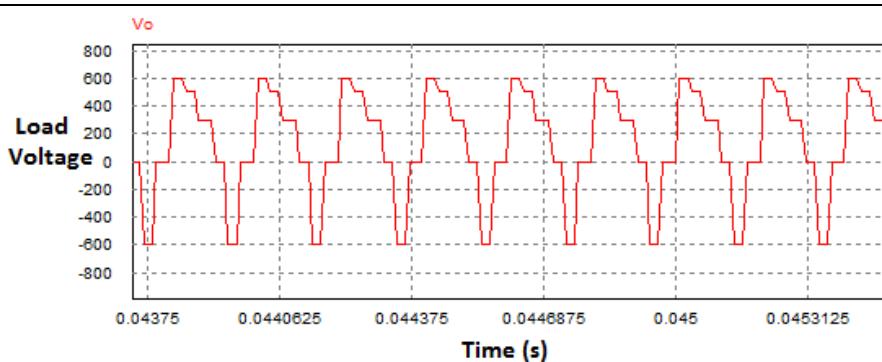

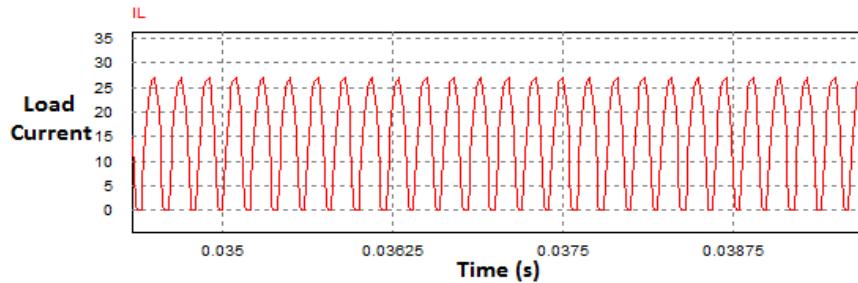

- **Asymmetrical Configuration-** The asymmetrical configuration of the HBMI produces an even higher number of output voltage levels, resulting in an even cleaner output waveform with lower THD. The simulation results demonstrate that the asymmetrical configuration can achieve superior harmonic performance compared to the symmetrical configuration, making it ideal for applications where power quality is critical. The voltage level are  $\pm 200$ ,  $\pm 400$  and  $\pm 600$  while the magnitude of current is observed as 27 A as shown in figure 4.3 and 4.4 respectively.

Figure 4.3: Output load voltage waveform (asymmetrical source)

Figure 4.4: Output load current waveform (asymmetrical source)

- Harmonic Analysis-** Harmonic analysis is a critical aspect of evaluating the performance of multilevel inverters. The simulation results for both configurations show a significant reduction in THD, with the asymmetrical configuration achieving the lowest THD. The harmonic spectrum analysis indicates that the HBMI effectively eliminates higher-order harmonics, resulting in a cleaner output waveform.

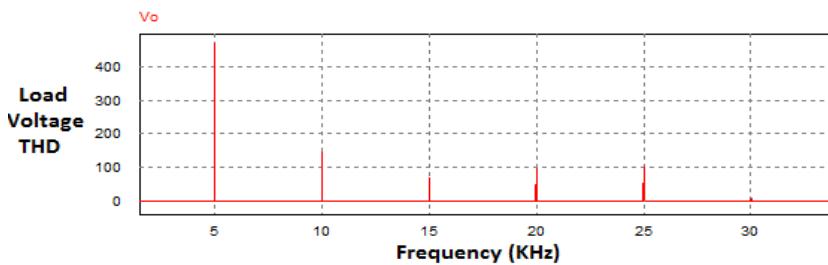

- Symmetrical Configuration-** The harmonic analysis for the symmetrical configuration shows that the dominant harmonics are at the switching frequency and its multiples. From the figure 4.5 and 4.6 the THD of the load voltage and load current is observed as 1% and 5% approximately.

Figure 4.5: Load voltage THD (symmetrical source)

Figure 4.6: Load Current THD (symmetrical source)

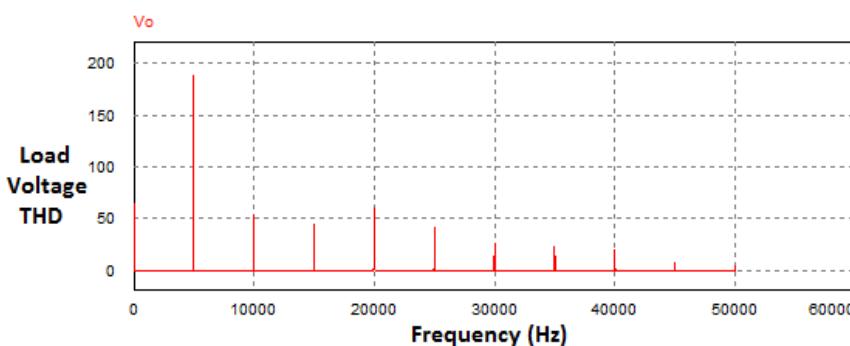

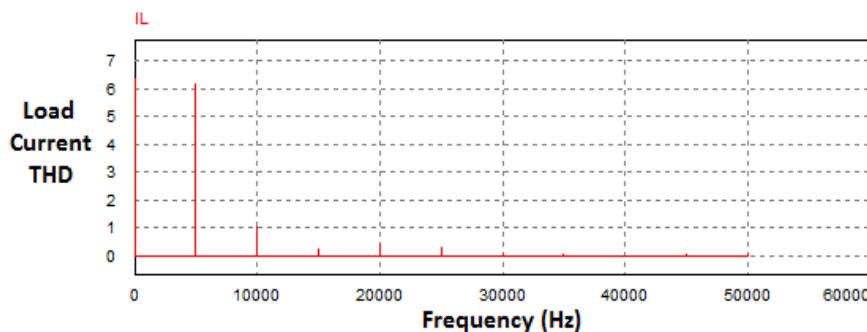

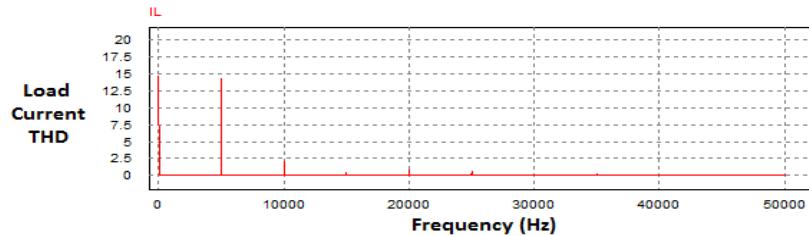

- Asymmetrical Configuration-** In the asymmetrical configuration, the harmonic performance is further improved due to the higher number of output voltage levels. From the figure 4.5 and 4.6 the THD of the load voltage and load current is observed as 4% and 15% approximately, with most of the harmonics concentrated at higher frequencies, which are easier to filter out.

**Figure 4.7:** Load voltage THD (asymmetrical source)

**Figure 4.8:** Load Current THD (asymmetrical source)

## 5. CONCLUSION

The Hybrid Bridge Multilevel Inverter (HBMI) topology offers a versatile and efficient solution for high-power applications, capable of accommodating both symmetrical and asymmetrical sources. The simulation results using PSIM software demonstrate the superior performance of the HBMI in terms of harmonic reduction, voltage stress distribution, and efficiency. The symmetrical configuration provides a simpler control strategy and high efficiency, while the asymmetrical configuration achieves even better harmonic performance at the cost of increased complexity.

## 6. REFERENCES

- [1] Burla, S., Dash, R., Shukla, S. P., & Dwivedi, A. (2023, September). Improved Gravitational Search Algorithm based Hysteresis controller for Grid integrated SPV system. In 2023 IEEE 2nd International Conference on Industrial Electronics: Developments & Applications (ICIDeA) (pp. 620-624). IEEE.

- [2] Chatteraj, J., Dwivedi, A., & Pahariya, D. Y. (2017). Enhancement of power quality in SAPS system with multilevel inverter. Int. J. Eng. Sci. Res. Technol., 6(5), 779-788.

- [3] Dwivedi, A. (2012). International Journal of Engineering Sciences & Management Benefits of Standalone Power Supply System. Int. J. of Engg. Sci. & Mgmt.(IJESM), 2(1), 62-65.

- [4] Dwivedi, A., & Pahariya, Y. (2017). Design and Analysis of 1.4 MW Hybrid Saps System for Rural Electrification in Off-Grid Applications. International Journal of Energy and Power Engineering 11(11) 1143-1147.

- [5] Dwivedi, A., & Pahariya, Y. (2018). Design of Continuous Mode Hybrid Standalone Power Station with Hybrid Controller to Select the Best Optimal Power Flow.

- [6] Dwivedi, A., & Pahariya, Y. (2021). Design and analysis of hybrid multilevel inverter for asymmetrical input voltages. Journal of Electrical Engineering & Technology, 16(6), 3025-3036.

- [7] Dwivedi, A., & Pahariya, Y. (2023). Techno-economic Feasibility Analysis of Optimized Stand-alone PV and Hybrid Energy Systems for Rural Electrification in INDIA. Journal of The Institution of Engineers (India): Series B, 104(4), 911-919.

- [8] Gautam SP, Kumar L, Gupta S (2015) Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electron 8(11):2125–213

- [9] Gupta KK, Ranjan A, Bhatnagar P, Kumar Sahu L, Jain S (2016) Multilevel inverter topologies with reduced device count: a review. IEEE Trans Power Electron 31(1):135–151.

- [10] Luo H, Dong Y, Li W, He X (2014) Module multilevel-clamped composited multilevel converter (M-MC2) with dual T-type modules and one diode module. Journal of Power Electron 14(6):1189–1196.

- [11] Pradeep Kumar VVS, Fernandes BG (2017) A fault tolerant single phase grid connected inverter topology with enhanced reliability for solar PV. IEEE J Emerg Si Power Electron 5(3):1254–1262.

- [12] Rajput, A.S., Dwivedi, A., Dwivedi, P., Rajput, D.S., Pattanaik, M. (2022). Read–Write Decoupled Single-Ended 9T SRAM Cell for Low Power Embedded Applications. In: Smys, S., Bestak, R., Palanisamy, R., Kotuliak, I. (eds) Computer Networks and Inventive Communication Technologies . Lecture Notes on Data Engineering and Communications Technologies, vol 75. Springer, Singapore.