## LOW-POWER RETENTIVE TRUE SINGLE-PHASE-CLOCKED FLIP-FLOP WITH REDUNDANT-PRECHARGE-FREE OPERATION

**Surampalli Dharani Mounica<sup>1</sup>, Manas Ranjan Biswal<sup>2</sup>**

<sup>1</sup>P. G. Scholor, Department of ECE, Sanketika Vidya Parishad Engineering College, Visakhapatnam, India.

<sup>2</sup>Assistant Professor, Department of ECE, Sanketika Vidya Parishad Engineering College, Visakhapatnam, India.

### ABSTRACT

As basic components, optimizing power consumption of flip-flops (FFs) can significantly reduce the power of digital systems. In this article, an energy-efficient retentive true-single-phase-clocked (TSPC) FF is proposed. With the employment of input-aware precharge scheme, the proposed TSPC FF precharges only when necessary. In addition, floating node analysis and transistor level optimization are employed to further ensure the high energy efficiency of the FF without significantly increasing the area. Post layout simulations based on SMIC 55-nm CMOS technology show that at a supply voltage of 1.2 V, the power consumption of the proposed FF is 84.37% lower than that of conventional transmission-gate flip-flop (TGFF) at 10% data activity. The reduction rate is increased to 98.53% as the data activity goes down to 0%. When the supply voltage decreases to 0.6 V, the proposed FF consumes only 0.411 fJ/cycle at 10% data activity, which is 84.23% lower than TGFF. Measurement results of ten test chips demonstrate the great energy efficiency of the proposed FF. Furthermore, the CK-to-Q delay of the proposed FF is 26.18% lower than that of TGFF at a supply voltage of 1.2 V.

### 1. INTRODUCTION

With the development of the process, the performance of digital system is greatly improved, and the power consumption is becoming an important limitation of digital systems. In addition, with the rapid development of the Internet of Things (IoT), IoT devices are deployed on a large scale [1]. In such battery-powered or self-powered devices, low-power design becomes the focus of attention [2]–[5]. As basic components, the power of flip-flops (FFs) accounts for a large part of the power of digital systems [6], [7]. Therefore, reducing the power consumption of FFs can significantly reduce the power consumption of the digital systems.

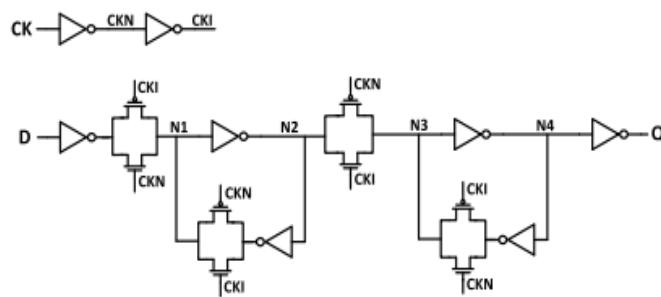

**Fig. 1.** Schematic of TGFF

Voltage-scaling technique has been proved to be an attractive method to decrease the power consumption of digital systems [8]–[12]. In order to obtain the power benefits of voltage-scaling technique, it is necessary to design an FF capable of operating at both super threshold and near/subthreshold supply voltage.

The transmission-gate flip-flop (TGFF) is the most widely used FF in current digital systems. The schematic of TGFF is shown in Fig. 1. The TGFF is a contention-free FF which is suitable for near-threshold operation. The main drawback of TGFF is the large clock network. The internal nodes CKN and CKI toggle no matter what the input data is, and the nodes CKN and CKI drive a larger number of transistors. Thus, the power consumption of TGFF is still large even if the data activity remains low. To reduce the power consumption of FF, the use of complementary clock signals should be optimized. Many low-power single-phase-clocked FFs have been proposed in previous works [13]–[18]. But there are still some problems that affect the power consumption of these FFs. For example, some of the FFs fail at low supply voltage [13]–[16], [18], and some suffer from large precharge power [13], [16]–[18]. In order to solve these problems, a low-power true-single-phase-clocked (TSPC) FF is proposed in this article. The proposed FF is contention-free and suitable for wide supply voltage operation. Furthermore, redundant precharge operation is totally removed in the proposed FF and the power consumption is further optimized compared with previous low-power FFs.

## 2. OBJECTIVE

In this paper, an energy-efficient retentive True Single-Phase-Clocked (TSPC) FF is proposed. With the employment of input-aware pre charge scheme, the proposed ITSPC FF pre charge only when necessary. By adopting this technique, power consumption is minimized.

## 3. PROPOSED METHODOLOGY

In this Paper, an energy efficient retentive true single-phase-clocked (TSPC) FF is proposed. As basic components, optimizing power consumption of flip-flops (FFs) can significantly reduce the power of digital systems. With the employment of input-aware precharge scheme, the proposed TSPC FF precharges only when necessary.

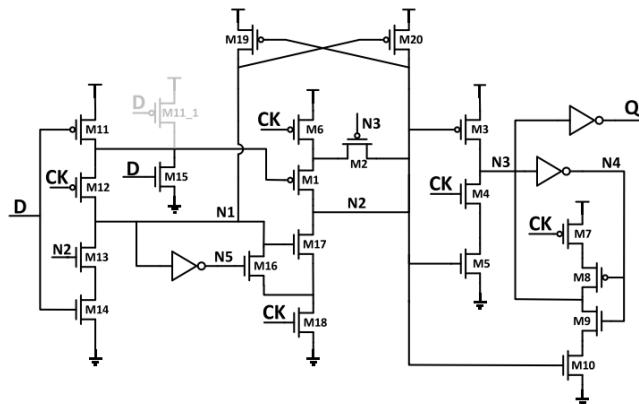

**Fig 2:** Schematic Design of the proposed TSPC FF

In addition, floating node analysis and transistor level optimization are employed to further ensure the high energy efficiency of the FF without significantly increasing the area. Later, the flip-flop is modified by adding SET, RESET scan inputs and finally a soft error tolerant Flip-flop is designed. The proposed designs are implemented in Tanner EDA/Cadence Virtuoso using 45mm technology file.

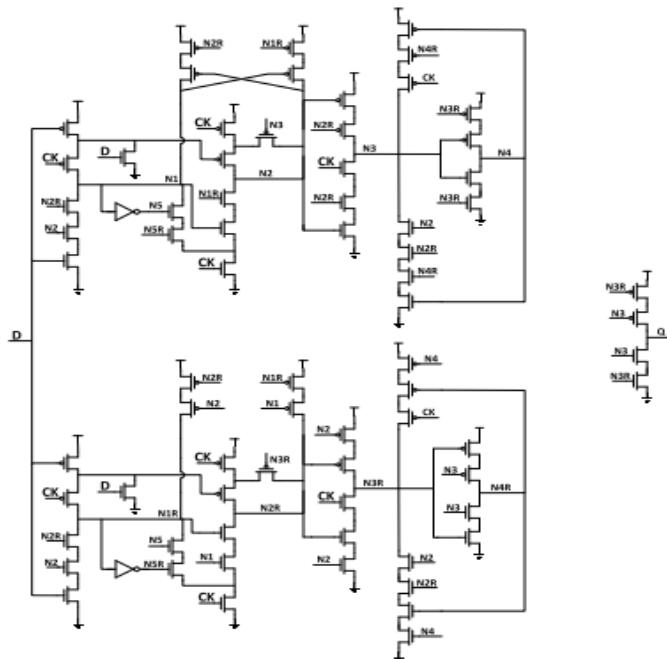

### 3.1 Design of Soft-Error Tolerant Optimization of the Proposed FF

Although scaling down the supply voltage can significantly decrease the power consumption of digital systems, aggressive voltage scaling will increase the soft error susceptibility of the systems [19]. In order to improve the stability of low-voltage systems, the proposed FF can be hardened to resist the single event effect (SEE), which includes single event upset (SEU) and single event transient (SET) [20]. The schematic of the proposed SEU-tolerant FF is shown figure below.

**Fig 3:** The schematic of the proposed SEU-tolerant FF is shown figure below

This is because when the voltage of N2 drops from VDD to GND due to an SEU, M3 and M19 are ON, the nodes N3 and N1 are charged to VDD, and the data stored in the FF is overwritten. Similarly, the nodes N1, N3, N4, and N5 in the proposed FF are all susceptible to SEUs. C-element-based logic has been proved to be an effective method for hardening [21]–[23]. By using C-element based logic, the proposed FF can be insensitive to SEUs.

#### 4. SIMULATION RESULTS

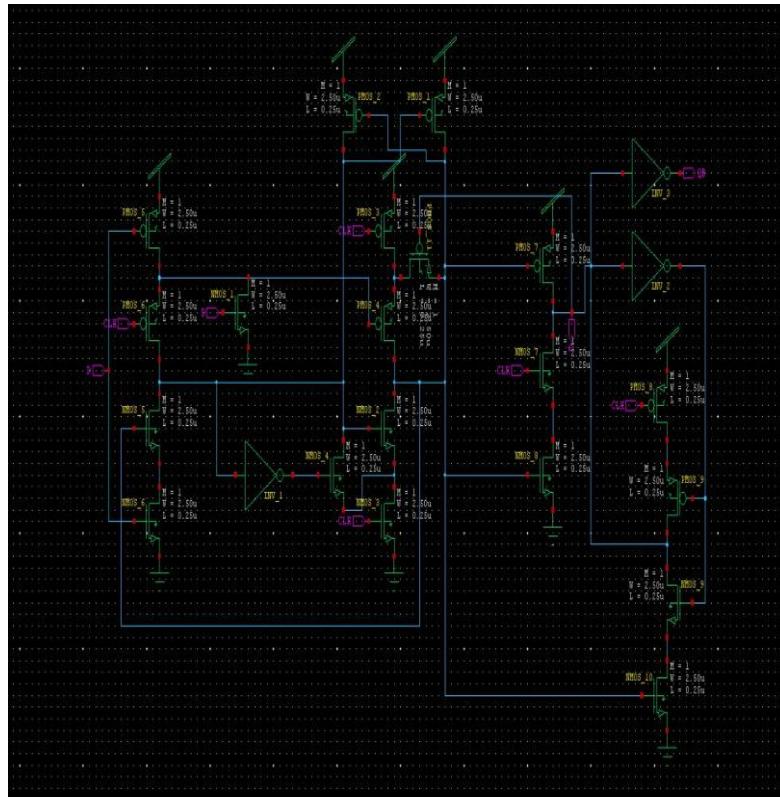

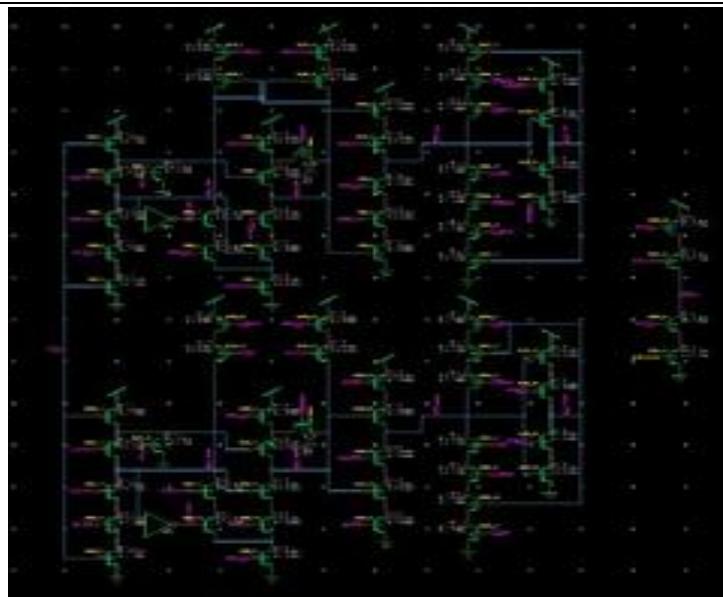

**Fig 4:** Schematic Diagram of True Single Phase Clocked FF (TSPCFF)

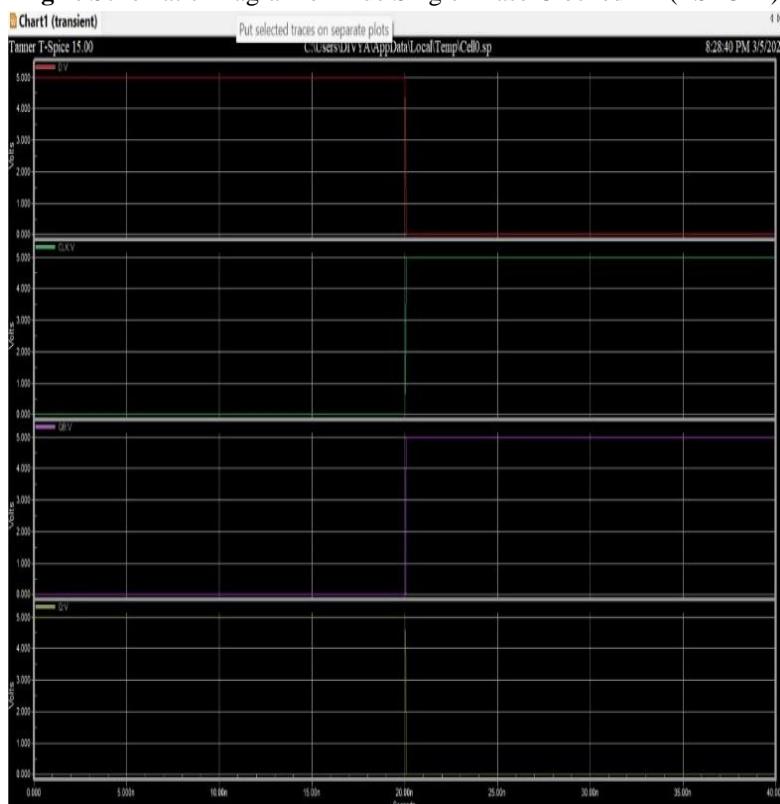

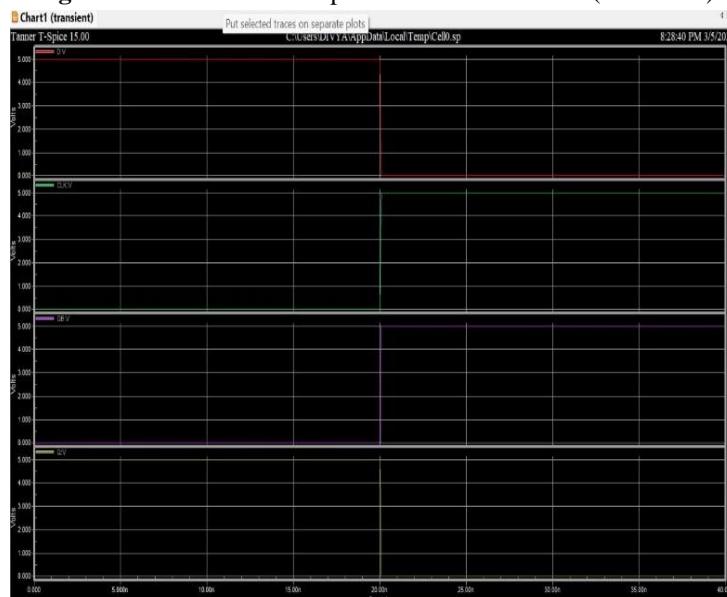

**Fig 5:** Output Waveform of True Single Phase Clocked FF (TSPCFF)

**Fig 6:** Schematic of the Proposed SEU-Tolerant FF (SEU-TFF)

**Fig 7:** Output Waveform of Proposed SEU-Tolerant FF (SEU-TFF)

## 5. CONCLUSION AND FUTURE SCOPE

### 5.1 CONCLUSION

An energy-efficient retentive TSPC FF was proposed. By removing redundant precharge and discharge operations with the input-aware precharge scheme, the power of the proposed FF is greatly reduced. Furthermore, floating node analysis is applied to the proposed structure to avoid the generation of short-circuit paths. Then, transistor level optimizations are applied to the circuit to further reduce the area and power consumption. Post layout simulation results show that the proposed FF saves more than 80% power consumption compared with TGFF under 10% data activity. Measurement results of ten test chips also demonstrate that the proposed FF has a significant energy efficiency improvement compared with TGFF. The CK-to-Q delay of the proposed FF is 26.18% lower than that of TGFF. The area of the proposed FF is just 4.8% larger than that of TGFF, indicating little area overhead to achieve such benefits.

### 5.2 FUTURE SCOPE

Further we would compare them and show that the counter designed with TSPC logic d flip-flop is less power consuming than other flip-flops. The circuit is then optimized at the transistor level to further reduce its size and power usage. According to post layout simulation results, the suggested FF consumes less power than TGFF with less than 10% data activity.

## 6. REFERENCES

- [1] L. Atzori, A. Iera, and G. Morabito, "The Internet of Things: A survey," *Comput. Netw.*, vol. 54, no. 15, pp. 2787–2805, Oct. 2010.

- [2] T. Tekeste, H. Saleh, B. Mohammad, A. Khandoker, and M. Ismail, "A nano-watt ECG feature extraction engine in 65-nm technology," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 8, pp. 1099–1103, Aug. 2018.

- [3] T. Tekeste, H. Saleh, B. Mohammad, and M. Ismail, "Ultra-low power QRS detection and ECG compression architecture for IoT healthcare devices," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 2, pp. 669–679, Feb. 2019.

- [4] A. Pullini, D. Rossi, I. Loi, G. Tagliavini, and L. Benini, "Mr. Wolf: An energy-precision scalable parallel ultra low power SoC for IoT edge processing," *IEEE J. Solid-State Circuits*, vol. 54, no. 7, pp. 1970–1981, Jul. 2019.

- [5] J. P. Cerqueira, T. J. Repetti, Y. Pu, S. Priyadarshi, M. A. Kim, and M. Seok, "Catena: A near-threshold, sub-0.4-mW, 16-core programmable spatial array accelerator for the ultralow-power mobile and embedded Internet of Things," *IEEE J. Solid-State Circuits*, vol. 55, no. 8, pp. 2270–2284, Aug. 2020.

- [6] J. L. Shin et al., "The next generation 64b SPARC core in a T4 SoC processor," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 82–90, Jan. 2013.

- [7] L. Moreau, R. Dekimpe, and D. Bol, "A 0.4 V 0.5fJ/cycle TSPC flipflop in 65 nm LP CMOS with retention mode controlled by clockgating cells," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2019, pp. 1–4.

- [8] A. Andrei, P. Eles, O. Jovanovic, M. Schmitz, J. Ogniewski, and Z. Peng, "Quasi-static voltage scaling for energy minimization with time constraints," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 19, no. 1, pp. 10–23, Jan. 2011.

- [9] X. Zhang et al., "32bit×32bit multiprecision razor-based dynamic voltage scaling multiplier with operands scheduler," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 22, no. 4, pp. 759–770, Apr. 2014.

- [10] W.-J. Tsou et al., "Digital low-dropout regulator with anti PVT-variation technique for dynamic voltage scaling and adaptive voltage scaling multicore processor," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 338–339.

- [11] S. Jain, L. Lin, and M. Alioto, "Dynamically adaptable pipeline for energy-efficient microarchitectures under wide voltage scaling," *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 632–641, Feb. 2018.

- [12] J. Lee et al., "A self-tuning IoT processor using leakage-ratio measurement for energy-optimal operation," *IEEE J. Solid-State Circuits*, vol. 55, no. 1, pp. 87–97, Jan. 2020.

- [13] A. Hirata, K. Nakanishi, M. Nozoe, and A. Miyoshi, "The cross chargecontrol flip-flop: A low-power and high-speed flip-flop suitable for mobile application SoCs," in *Dig. Tech. Papers. Symp. VLSI Circuits*, Jun. 2005, pp. 306–307.

- [14] C. K. Teh, T. Fujita, H. Hara, and M. Hamada, "A 77% energy-saving 22-transistor single-phase-clocking D-flip-flop with adaptive-coupling configuration in 40 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 338–339.

- [15] N. Kawai et al., "A fully static topologically-compressed 21-transistor flip-flop with 75% power saving," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2526–2533, Nov. 2014.

- [16] Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell, and T. J. Kazmierski, "Ultra-low power 18-transistor fully static contentionfree single-phase clocked flip-flop in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 2, pp. 550–559, Feb. 2019.

- [17] Y. Kim et al., "A static contention-free single-phase-clocked 24T flip flop in 45 nm for low-power applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 466–467.

- [18] F. Stas and D. Bol, "A 0.4-V 0.66-fJ/cycle retentive true-single-phaseclock 18T flip-flop in 28-nm fully-depleted SOI CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 3, pp. 935–945, Mar. 2018.

- [19] F. S. Alghareb, R. A. Ashraf, and R. F. DeMara, "Designing and evaluating redundancy-based soft-error masking on a continuum of energy versus robustness," *IEEE Trans. Sustain. Comput.*, vol. 3, no. 3, pp. 139–152, Jul. 2018.