editor@ijprems.com

INTERNATIONAL JOURNAL OF PROGRESSIVE<br/>e-ISSN :RESEARCH IN ENGINEERING MANAGEMENT<br/>AND SCIENCE (IJPREMS)2583-1062(Int Peer Reviewed Journal)Impact<br/>Factor :Vol. 04, Issue 10, October 2024, pp : 1329-13327.001

### DESIGN OF 8-BIT APPROXIMATE MULTIPLIER USING SINGLE EXACT SINGLE APPROXIMATE ADDERS AND SINGLE EXACT DUAL APPROXIMATE ADDERS

#### Rangoori Sravani Sai<sup>1</sup>, Ananda Kumari<sup>2</sup>

<sup>1</sup>P.G Scholor, Sanketika Vidya Parishad Engineering College, Visakhapatnam, India.

<sup>2</sup>Assistant Professor, Sanketika Vidya Parishad Engineering College, Visakhapatnam, India. sravanisairangoori@gmail.com, anandaniigatti18@gmail.com DOI: https://www.doi.org/10.58257/IJPREMS36495

#### ABSTRACT

An adder is the basic computational circuit in digital Very Large Scale Integration design. Approximate Adders have been proposed to improve the design metrics of an adder. Digital Multiplier is a fundamental component in many digital signal processing (DSP) systems, which takes up the most part of the computational resources. As many DSP applications have an inherent tolerance for inexact computations, approximate multiplication is considered as an appropriate substitution to obtain energy-performance-accuracy tradeoffs, especially in those applications that require high energy-efficiency in computing. Meanwhile, reducing the supply voltage is proved to be an efficient way to further lower the total energy consumption. In this paper multiplexer based approximate full adder is proposed for 8-Bit approximate multiplier and its circuit implementation is proposed for error-resilient multiplication with a low supply voltage. Simulation results indicate that the approximate multiplier with our proposed 8-Bit approximate multipliers for the operand length of 8 bits. It achieves 26.7% reduction on energy-delay product (EDP) when compared with the exact multiplication.

Keywords- Single Exact Single Approximate Adder, Single Exact Dual Approximate Adder, Approximate Multiplier, Power consumption, propagation delay.

#### 1. INTRODUCTION

Computing efficiency of the adder with new circuit designs provides high performance and better result [2]. One of the recent [1] and efficient method is approximate computing. It is being used in many applications like computer vision, data mining, deep learning neural networks, video/image processing etc [3,4]. Approximate computing gives results which are less accurate but with acceptable quality by providing the stringent error requirement. Digital multipliers are always fundamental arithmetic units with important influence on performance of the entire system. A fast multiplier is typically composed of three parts: partial products generation, partial products compression, and a fast carry propagation adder (CPA) for the result. Among these three parts, the compression tree occupies the largest proportion in terms of area, delay and power consumption. Thus, energy efficient compressors are required in the multiplier design Intuitively, the partial products in a compression tree are accumulated with two operand adders, which use full adders, sometimes known as 3-2 compressors. Compared with full adders, 8-Bit approximate multiplier have a higher compression efficiency so that are widely used in a partial products reduction tree. In approximate multiplier design, many approximate 8-Bit approximate multiplier have been proposed to achieve high energy efficiency [3]-[6]. An approximation method is proposed in [3], which cuts the carry chains between two 8-Bit approximate multiplier of the same stage. It reduces the hardware complexity greatly but incurs a high error rate, and thus, a poor computational accuracy. In this paper, a multiplexer approximate adder based approximate 4-2 compressor is proposed with a complementary error strategy in order to obtain a reduced logic complexity with acceptable computation accuracy. In addition, the circuits are designed at a low supply voltage to achieve even higher energy efficiency.

#### 2. EXISTING TECHNIQUES

#### 2.1 SESA1 ADDER

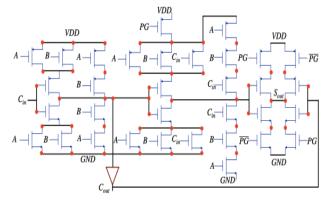

In SESA1 adder, we introduce approximation in the SUM output by making it to be equal to the complement of CARRY. As seen from Table, SESA1 adder has errors in SUM bits for input combinations 000 and 111. The CARRY output remains same irrespective of whether SESA1 adder operates in exact or approximate mode. In exact mode, the SUM output is computed using a power gated (PG) controlled inverter whose input is the complement of SUM. In approximate mode, the SUM module is PG, and the approximate output which is made equal to the complement of CARRY is generated using another PG-controlled inverter whose input is connected to the complement of CARRY as shown in Figure.

editor@ijprems.com

## INTERNATIONAL JOURNAL OF PROGRESSIVEe-JRESEARCH IN ENGINEERING MANAGEMENT258AND SCIENCE (IJPREMS)In(Int Peer Reviewed Journal)Fa

e-ISSN : 2583-1062 Impact Factor : 7.001

Vol. 04, Issue 10, October 2024, pp : 1329-1332

Figure 1: Circuit diagram of SESA1 adder

#### 2.2 SESA2 ADDER

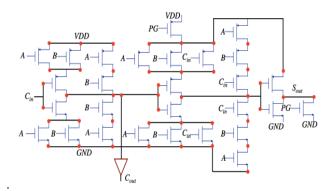

In SESA2 adder, we introduce approximation in the SUM output by making it 0 for all the input combinations as shown in Table for approximate mode.

Figure 2: Circuit diagram of SESA2 adder

As a result of this, SESA2 adder has errors in SUM bits for input combinations 001, 010, 100, and 111. The CARRY output remains same irrespective of whether SESA2 adder operates in exact or approximate mode. In exact mode, the SUM output is computed using the normal SUM module. In approximate mode, the SUM module is PG and the approximate output which is equal to 0 is generated using a PG-controlled NMOS that pulls down the SUM output to a 0 as shown in Figure.

#### 2.3 SESA3 ADDER

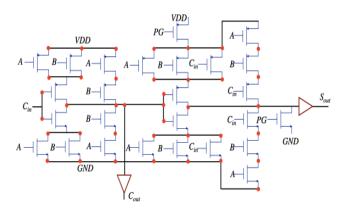

In SESA3 adder, we introduce approximation in the SUM output by making it 1 for all the input combinations as shown in Table II. As a result of this, SESA3 adder has errors in SUM bits for input combinations 000, 011, 101, and 110. The CARRY output remains same irrespective of whether SESA3 adder operates in exact or approximate mode. In exact mode, the SUM output is computed using the normal SUM module. In approximate mode, the SUM module is PG and the approximate output which is equal to 1 is generated using a PG-controlled NMOS that pulls down the complement of SUM to a permanent 0. Since this is connected to an inverter, we get the SUM output in approximate mode to be a 1 as shown in Figure.

Figure 3: Circuit diagram of SESA3 adder

| ERNATIONAL JOURNAL OF PROGRESSIVE               | e-ISSN :                                                                                 |

|-------------------------------------------------|------------------------------------------------------------------------------------------|

| SEARCH IN ENGINEERING MANAGEMENT                | 2583-1062                                                                                |

| AND SCIENCE (IJPREMS)                           | Impact                                                                                   |

| (Int Peer Reviewed Journal)                     | Factor :                                                                                 |

| Vol. 04, Issue 10, October 2024, pp : 1329-1332 | 7.001                                                                                    |

|                                                 | SEARCH IN ENGINEERING MANAGEMENT<br>AND SCIENCE (IJPREMS)<br>(Int Peer Reviewed Journal) |

#### 3. PROPOSED WORK

#### **3.1 SEDA ADDER**

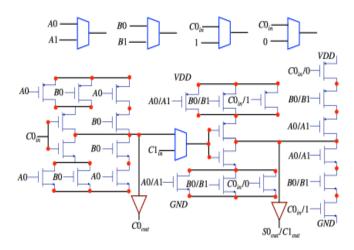

The SEDA adders surpasses the SESA adder in terms of advancement. Additionally, it possesses a maximum limit on the potential inaccuracy and offers the possibility to be customized. In contrast to SESA adders, which are limited to performing only one approximate addition, SEDA adders have the capability to do two approximate additions when operating in approximation mode. In the framework of SESA, we implement power gating for the SUM module of the adder, particularly when it is used in approximation mode. This is done in order to ensure safety and efficiency. Additionally, the SUM module is utilized within the SEDA adder in order to generate an extra CARRY.

Figure 4: Circuit diagram of SEDA adder

#### 3.2 8-Bit Approximate Multiplier

The number of stages of the proposed multiplier is one stage less than that of the former. At the last stage of the proposed multiplier, in order to obtain the summation of the three remaining rows of partial product, an especial CPA is used which was constructed by some half adders and some proposed approximate compressors. In each of the columns 2 and 15 of this CPA, a half adder is used, and in each of the columns 3 to 14, the first proposed compressor is used. Indeed, columns 3-14 of this CPA is our proposed CPA introduced in the previous sub-section which does not have the carry propagate delay problem

Figure 6: Approximate Multiplier

The proposed multiplier shown each rectangle represents a half adder or a full adder. Sum of the last stage's columns are computed using a CPA which is constructed by some half adders, full-adders, and proposed 4:2 compressors.

# INTERNATIONAL JOURNAL OF PROGRESSIVE<br/>RESEARCH IN ENGINEERING MANAGEMENT<br/>AND SCIENCE (IJPREMS)e-ISSN :<br/>2583-1062AND SCIENCE (IJPREMS)Impact<br/>Factor :(Int Peer Reviewed Journal)Factor :<br/>7.001

#### 4. SIMULATION RESULTS

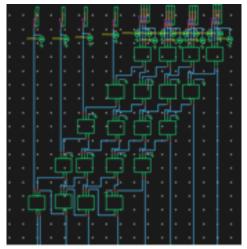

Figure 7: Approximate Multiplier using 4:2 Compressor

#### 5. CONCLUSION

The design of a 4:2 compressor using single exact single approximate adders and single exact dual approximate adders has demonstrated the potential of approximate computing in achieving improved power efficiency and area reduction with minimal accuracy trade-offs. The approach leverages the concept of approximate adders to optimize the compressor design, making it suitable for applications where absolute precision is less critical. Approximate adders minimize the number of switching events and reduce overall capacitance, resulting in lower dynamic power requirements. This makes the design highly suitable for power-sensitive applications, such as embedded systems and IoT devices. The design shows a marked reduction in transistor count and layout area compared to traditional exact-only designs. Using approximate adders reduces the number of required logic elements, allowing for a more compact layout that is advantageous in high-density integrated circuits. The simplified logic in approximate adders contributes to reduced propagation delay, enhancing the overall speed of the compressor. This speed improvement makes the design appropriate for high-speed applications where minor accuracy trade-offs are acceptable, such as image and signal processing.

#### 6. REFERENCE

- Q. Xu, T. Mytkowicz, and N. S. Kim, "Approximate computing: A survey," IEEE Des. Test, vol. 33, no. 1, pp. 8– 22, Feb. 2016.

- [2] C.-H. Chang, J. Gu, and M. Zhang, "Ultra low-voltage low- power CMOS 4-2 and 5-2 compressors for fast arithmetic circuits," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 10, pp. 1985–1997, Oct. 2004.

- [3] A. Momeni, J. Han, P. Montuschi and F. Lombardi. "Design and Analysis of Approximate Compressors for Multiplication," IEEE Trans. Comput., vol.64, no.4, pp. 984-994, Apr. 2015.

- [4] L. Qian, C. Wang, W. Liu, F. Lombardi and J. Han, "Design and evaluation of an approximate Wallace-Booth multiplier," 2016 IEEE Int. Symp. Circuits Syst. (ISCAS), Montreal, QC, 2016, pp. 1974-1977.

- [5] Z. Yang, J. Han and F. Lombardi. "Approximate compressor for error resilient multiplier design," IEEE Int. Symp. On Defect Fault Tolerance in VLSI and Nano. Syst., MA, USA, Oct. 2015.

- [6] S. Venkatachalam and S.-B. Ko, "Design of power and area efficient approximate multipliers," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 5, pp. 1782–1786, May 2017.

- [7] J. Jun, J. Song and C. Kim, "A Near-Threshold Voltage Oriented Digital Cell Library for High-Energy Efficiency and Optimized Performance in 65nm CMOS Process," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 65, no. 5, pp. 1567-1580, May 2018.

- [8] M. Aliotto, "Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 1, pp. 3–29, January 2012.

- [9] Z. Zhang, Y. He, "A Low Error Energy-Efficient Fixed-Width Booth Multiplier with Sign-Digit-Based Conditional Probability Estimation," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 65, no. 2, pp. 236–240, May. 2017.

- [10] V. Garofalo, N. Petra and E. Napoli, "Analytical Calculation of the Maximum Error for a Family of Truncated Multipliers Providing Minimum Mean Square Error," IEEE Trans. Comput., vol. 60, no. 9, pp. 1366-1371, Sept. 2011.) Systems, pp. 566-581, 2002.