e-ISSN : 2583-1062 Impact Factor :

5.725

www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

## DESIGN AND PREDICTION OF FUTURE BEHAVIOUR OF COMBINATIONAL LOGIC CIRCUIT AND FSM USING ARTIFICIAL NEURAL NETWORK

## Sudhanshu Yadav<sup>1</sup>, Prof. Ranu Thakur<sup>2</sup>

<sup>1</sup>Mtech scholar, Department of EC Engineering, LNCT (Bhopal) Indore Campus, Indore (M.P.), India. <sup>2</sup>Assistant professor, Department of EC Engineering, LNCT (Bhopal) Indore Campus, Indore (M.P.), India.

## ABSTRACT

The design and testing of digital circuits and systems has undergone a paradigm shift in recent times with the advent of artificial intelligence. It was customary to design digital circuits using the knowledge of the internal circuitry or the input-output mapping or truth table of the circuit. Some modern applications though need interactive behavior from systems which finally boils down to the interactive design of digital circuits. Some example can be the internal circuitry of interactive gaming consoles, vending machines, sequence detectors, human machine interfaces (HMI) etc. The aim is to design an Artificial Intelligence based system which would get trained using the limited input-output mapping of the circuit and be able to predict the future behavior of the circuit.

#### 1. INTRODUCTION

#### **1.1 DIGITAL CIRCUIT DESIGN**

The basic building blocks of digital circuits are Gates. Gates can be thought of as entities which take logic 0 or 1 as input combinations and yield an output depending on the logical operation on the inputs. Needless to say, the output is also in the form of 0 and 1. Logic gates serve as the basic building block for digital circuits. Digital circuits can be broadly classified as:

- 1) Combinational Circuits.

- 2) Sequential Circuits.

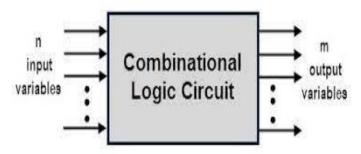

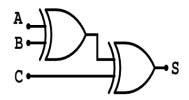

1.1.1 Combinational Circuit:-A combinational circuit is the digital logic circuit in which the output depends on the combination of inputs at that point of time with total disregard to the past state of the inputs. The digital logic gate is the building block of combinational circuits

Figure1 - Combinational Circuit

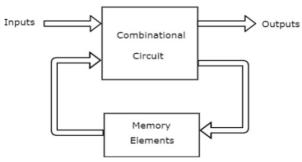

1.1.2 Sequential Circuit:- The sequential circuit is a special type of circuit that has a series of inputs and outputs. The outputs of the sequential circuits depend on both the combination of present inputs and previous outputs. The previous output is treated as the present state

www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

#### **1.2 FINITE STATE MACHINES**

State machines are a method of modeling systems whose output depends on the entire history of their inputs, and not just on the most recent input. State machines can be used to model a wide variety of systems, including:

- user interfaces, with typed input, mouse clicks, etc.;

- conversations, in which, for example, the meaning of a word "it" depends on the history of things that have been said;

- the state of a spacecraft, including which valves are open and closed, the levels of fuel and oxygen, etc.; and

- the sequential patterns in DNA and what they mean.

State machine models can either be continuous time or discrete time. In continuous time models, we typically assume continuous spaces for the range of values of inputs and outputs, and use differential equations to describe the system's dynamics.

#### **1.2.1 Primitive state machines**

We can specify a transducer (a process that takes as input a sequence of values which serve as inputs to the state machine, and returns as output the set of outputs of the machine for each input) as a state machine (SM) by specifying:

- a set of states, S,

- a set of inputs, I, also called the input vocabulary,

- a set of outputs, O, also called the output vocabulary,

- a next-state function,  $n(i_t, s_t) \rightarrow s_{t+1}$ , that maps the input at time t and the state at time t to the state at time t + 1,

- an output function,  $o(i_t, s_t) \rightarrow o_t$ , that maps the input at time t and the state at time t to the output at time t; and

- an initial state, s<sub>0</sub>, which is the state at time 0.

#### 1.2.2 Mealy Machine

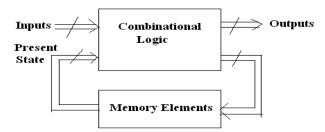

In this model of FSM, the output values are determined both by its current state and the current inputs. In the figure 1.2 it is shown that the input is fed to the combinational circuit C1 and then a state register is used to store the output of C1. The input and the output of the register fed to the second combinational circuit C2. Hence the output is determined both by present state and input.

Figure 3. Mealy Type Machine

Figure.3

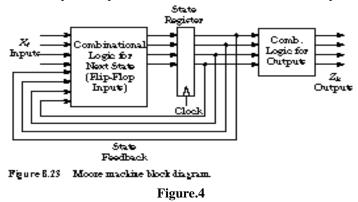

#### **1.2.2 Moore Machine**

A Moore machine is a finite-state machine whose current output values are determined only by its current state. This is in contrast to a Mealy machine, whose output values are determined both by its current state and by the values of its inputs. Like other finite state machines, in Moore machines, the input typically influences the next state. Thus the input may indirectly influence subsequent outputs, but not the current or immediate output.

e-ISSN: 2583-1062 Impact **Factor**:

www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

5.725

#### 2. PROBLEM DOMAIN

Conventionally, all digital circuits are designed by the following to techniques:

1) Prior knowledge of the internal circuitry. For example consider the circuit diagram of a half adder circuit

Figure5. Internal Circuitry of a Half Adder

2) Input – Output mapping of the circuit also called the Truth-

Table.1

|       | Truth | Table  |       |

|-------|-------|--------|-------|

| Input |       | Output |       |

| Α     | В     | Sum    | Carry |

| 0     | 0     | 0      | 0     |

| 0     | 1     | 1      | 0     |

| 1     | 0     | 1      | 0     |

| 1     | 1     | 0      | 1     |

In both the cases, either the internal circuit or the input-output mapping of the circuit was known which meant circuit design would be possible following standard design steps. The major challenge arrives when neither the internal circuit nor the truth table of the circuit is known but only certain input output mapping pairs are known which tend to change. In such cases, it becomes extremely complex to predict the behavior of the circuit. Such applications are needed in human machine interfaces (HMI) and interactive systems.

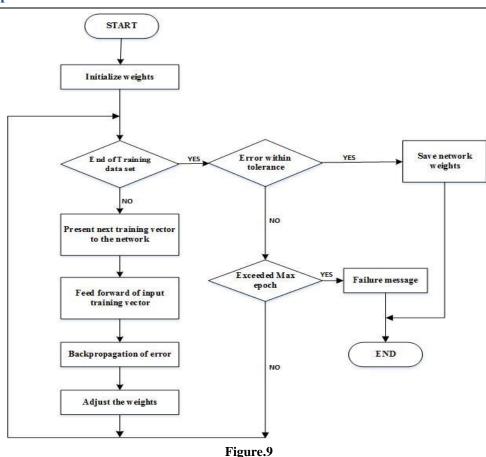

The design of such systems requires the need of Artificial Intelligence. There are several AI based algorithms that can be utilized for the design and prediction of digital circuits. We mainly focus on systems with feedback or systems with **Back Propagation.**

## 3. SOLUTION DOMAIN AND PROPOSED METHODOLOGY

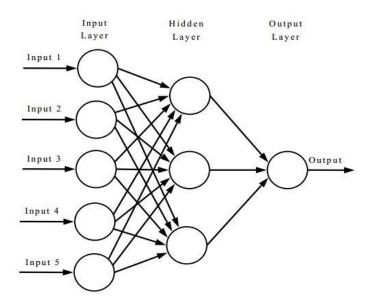

#### 2.1 ANN (Artificial Neural Networks):-

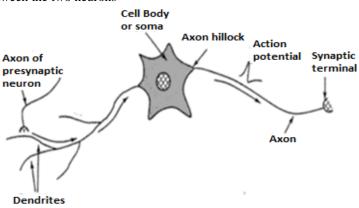

Artificial Neural Networks (ANN) are computing systems or technique that are inspired by the learning architecture of human brain to discover the relations between the input and target variables of a system. Neurons are simple processing units, which has the ability to store experimental data and which work as parallely distributed processor.

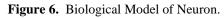

The axon works as a transmitter of the neuron. It sends signals to neighbouring neurons. The synapse or synaptic terminal are the connection between the axon of one neuron and the dendrites of neighbouring neutron, which is the communication link in between the two neurons

Consider a signals<sub>1</sub> travelling through a path  $p_1$  from dendrites with weight  $w_1$  to the neuron. Then the value of signal reaching the neuron will  $bes_1$ .  $w_1$ . If there are "n" such signals travelling through n different paths with weights ranging from  $w_1$  to  $w_n$  and the neuron has an internal firing threshold value of  $\theta_n$ , then the total activation function of the neuron isgiven by:

www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

TCCN .

$$y = \sum_{i=1}^{n} X_i . W_i + \theta_i (4.1)$$

HereX<sub>i</sub> represents the signals arriving through various paths,

$W_i$  represents the weight corresponding to the various paths and  $\theta$  is the bias. The entire mathematical model of the neuron or the neural network can be visualized pictorially or the pictorial model can be mathematically modelled. The design of the neural network can be modelled mathematically and the more complex the neural design, more is the complexity of the tasks that can be accomplished by the neural network. The above concept can be visualized by the following diagram:

Figure 7: The mathematical formulation of the neural model.

ANN poses great ability to train itself based on the data provided to it for initial training. It has the tendency of selforganization during learning period and it can perform during real time operation.

Figure 8: Working model of an ANN

#### **3.2 BACK PROPAGATION**

Although the weights of a neural network tend to make subsequent error plummet, yet the rate at which the error reduces is critical in real time systems. Hence, it is prudent enough to design a system in which errors are fed back to the system in order to make it realize the amount of error present in every iteration. This technique is called back propagation.

e-ISSN : 2583-1062 Impact

www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

Impact Factor : 5.725

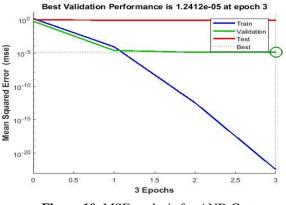

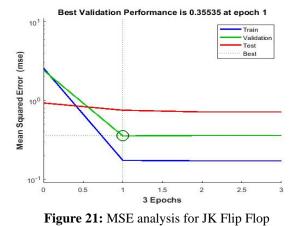

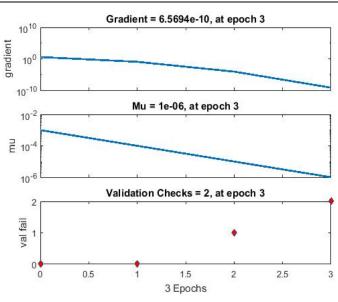

#### 4. RESULTS

Before proceeding towards complex FSMs, we start our discussion with the design and implementation of logic gates. Subsequently, we move on to the design of combinational circuits, sequential circuits and finally sequence detectors.

The circuits simulated are:

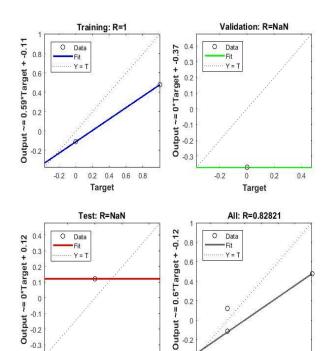

- 1. AND GATE using LM Algorithm

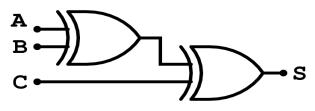

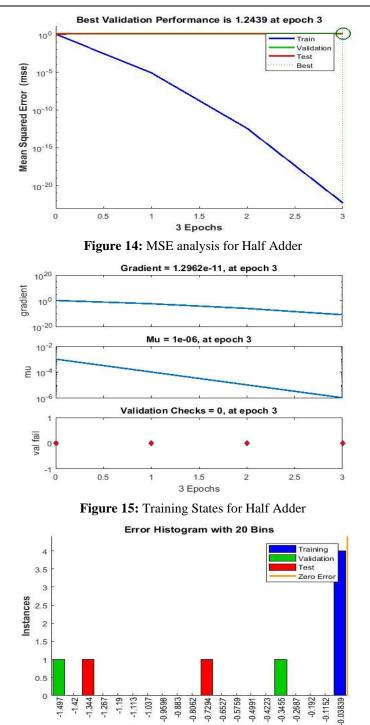

- 2. HALF ADDER using LM Algorithm

- 3. JK FLIP FLOP using LM Algorithm

- 4. A Jordan network implementation of the Half Adder

- 5. Sequence detector design using LM, BR and SCG algorithms.

- 6. The performance indices considered here are:

- 1) Mean Square Error (MSE)

- 2) Epochs or execution time

- 3) Iterations

- 4) Error Histograms for Graphical Error Representation

- 5) Regression

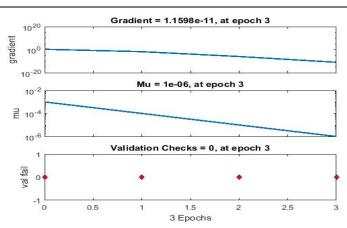

Figure 10. MSE analysis for AND Gate

e-ISSN: 2583-1062 Impact Factor :

#### www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

5.725

Figure 11: Training States for AND Gate

0.4

0.2

Target

-0.2 0 -0.2

0 0.2 0.4

Target

0.6 0.8

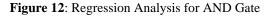

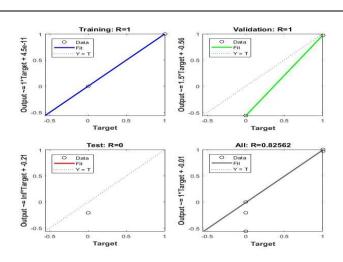

#### 4.2 Half Adder

Figure 13: Logic Diagram of Half Adder Table. 2. Truth Table for Half Adder

|       | Truth | Table  |       |

|-------|-------|--------|-------|

| Input |       | Output |       |

| A     | В     | Sum    | Carry |

| 0     | 0     | 0      | 0     |

| 0     | 1     | 1      | 0     |

| 1     | 0     | 1      | 0     |

| 1     | 1     | 0      | 1     |

e-ISSN : 2583-1062 Impact Factor : 5.725

#### www.ijprems.com editor@ijprems.com

#### Vol. 03, Issue 12, December 2023, pp : 77-86

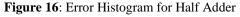

Errors = Targets - Outputs

Figure 17: Neural Network Design for Half Adder

e-ISSN: 2583-1062 Impact Factor :

## www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

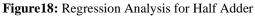

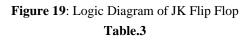

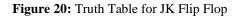

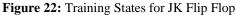

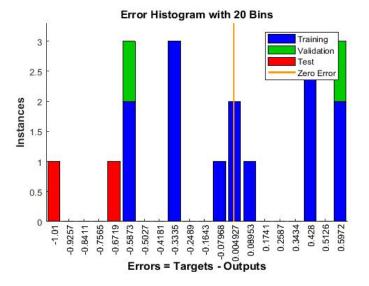

#### 4.3 JK Flip Flop:

| Q | J | к | Q(t+1) |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

@International Journal Of Progressive Research In Engineering Management And Science

e-ISSN : 2583-1062 Impact Factor : 5.725

#### www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

| Neural Network Training (nntraintool)                                                                                                    |                                                                                  | _ @ X               |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|

| Neural Network                                                                                                                           |                                                                                  |                     |

|                                                                                                                                          | hppt<br>3<br>20<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                     |

| Algorithms                                                                                                                               |                                                                                  |                     |

| Data Division: Random (dividerand)   Training: Levenberg-Marquardt (trainlm)   Performance: Mean Squared Error (mse)   Calculations: MEX |                                                                                  |                     |

| Progress                                                                                                                                 |                                                                                  |                     |

| Epoch: 0 3 iterations                                                                                                                    | 1000                                                                             |                     |

| Time: 0:00:05                                                                                                                            |                                                                                  |                     |

| Performance: 0.772 0.171                                                                                                                 | 0.00                                                                             |                     |

| Gradient: 1.61 2.85e-11                                                                                                                  | 1.00e-07                                                                         |                     |

| Mu: 0.00100 1.00e-06                                                                                                                     | 1.00e+10                                                                         |                     |

| Validation Checks: 0                                                                                                                     | 6                                                                                |                     |

| Plots                                                                                                                                    |                                                                                  |                     |

| Performance (plotperform)                                                                                                                |                                                                                  |                     |

| Training State (plottrainstate)                                                                                                          |                                                                                  |                     |

| Error Histogram (ploterrhist)                                                                                                            |                                                                                  |                     |

| Regression (plotregression)                                                                                                              |                                                                                  |                     |

| Fit (plotfit)                                                                                                                            |                                                                                  |                     |

|                                                                                                                                          | Plot Interval:                                                                   |                     |

| Minimum gradient reached.                                                                                                                |                                                                                  |                     |

|                                                                                                                                          |                                                                                  | top Training Cancel |

|                                                                                                                                          |                                                                                  |                     |

e-ISSN : 2583-1062 Impact Factor : 5.725

## www.ijprems.com editor@ijprems.com

Vol. 03, Issue 12, December 2023, pp : 77-86

Figure 25: Regression Analysis for JK Flip Flop

## 5. CONCLUSION

It can be concluded from the previous discussions that the design and prediction of complex digital circuits is possible using Artificial Neural Networks (ANN). The benefit of such a system lies in the fact that there is no need of knowing the internal circuitry or the complete input output mapping of the digital system to predict its performance. The behavior of the circuit can be predicted by the ANN based system once the system has been trained. This approach finds extensive application in interactive gaming, Human Machine Interfaces (HMI), hardware level cryptography.

## 6. FUTURE SCOPE

The future scope can be thought of as in improving and optimizing the present algorithms to attain even better performance indices such as lesser number of iterations, better regression and lesser MSE. Also the design of cascaded algorithmic structures can be designed to while retaining the merits of each of the algorithms. Also, more complex circuits can be tested in real time applications.

## 7. REFERENCES

- [1] State assignment for area minimization of sequential circuits based on cuckoo search optimization q Aiman H. El-Maleh, Sadiq M. Sait, AbubakarBala Elsevier 2015

- [2] VLSI Implementation of Deep Neural Network Using Integral Stochastic Computing ArashArdakani, Student Member, IEEE, François Leduc-Primeau, NaoyaOnizawa, Member, IEEE, Takahiro Hanyu, Senior Member, IEEE and Warren J. Gross, Senior Member, IEEE 2016

- [3] Memristor-Based Cellular Nonlinear/Neural Network: Design, Analysis, and Applications ShukaiDuan, Member, IEEE, Xiaofang Hu, Student Member, IEEE, Zhekang Dong, Student member, IEEE Transaction 2015

- [4] A Synthesis Flow for Sequential Reversible Circuits Mathias Soeken\_ Robert Wille\_ Christian Otterstedt\_ Rolf Drechsler, IEEE 2014

- [5] On adaptive experiments for nondeterministic finite state machines Natalia Kushik · Khaled El-Fakih · Nina Yevtushenko · Ana R. Cavalli, Springer 2014

- [6] Deep Learning in Neural Networks: An Overview Technical Report IDSIA-03-14 / arXiv:1404.7828 v4 [cs.NE] (88 pages, 888 references) J<sup>\*</sup>urgenSchmidhuber The Swiss AI Lab IDSIA IstitutoDalleMolle di Studisull'IntelligenzaArtificiale, IEEE 2014

- [7] Low-Power Analysis of VLSI Circuit Using Efficient Techniques P.Rahul Reddy1, D.Prasad2, IJNTSE 2015

- [8] Finite-state computation in analog neural networks: steps towards biologically plausible models?Mikel L. Forcada and Rafael C. Carrasco, Springer 2012

www.ijprems.com

editor@ijprems.com

## e-ISSN: INTERNATIONAL JOURNAL OF PROGRESSIVE **RESEARCH IN ENGINEERING MANAGEMENT** AND SCIENCE (IJPREMS)

Vol. 03, Issue 12, December 2023, pp : 77-86

[9] Backpropagation and Levenberg-Marquardt Algorithm for Training Finite Element Neural Network Arnold Reynaldi\*, Samuel Lukas<sup>†</sup>, Helena Margaretha\*, IEEE 2012

Predictive Abilities of Bayesian Regularization andLevenberg-Marquardt Algorithms in Artificial Neural [10] Networks: A Comparative Empirical Study on Social Data Murat Kayri, MDPI, 2016

- [11] A Scaled Conjugate Gradient Algorithm for Fast Supervised Learning Martin F. Møller Computer Science Department, Springer 2010

- [12] Jordan Neural Network for Modelling and Predictive Control of Dynamic Systems AntoniWysocki and MaciejŁawry'nczuk, IEEE 2015

- [13] Weighting Finite-State TransductionsWith Neural Context PushpendreRastogi and Ryan Cotterell and Jason Eisner, NAACL-HLT Proceedings 2016

- [14] Recurrent Neural Networks: State Machines and Pushdown Automata C. Lee Giles, Alexander Ororbia II The Pennsylvania State University University Park, PA, USA giles@ist.psu.edu http://clgiles.ist.psu.edu

- [15] Desig n and Implementation of Neural Network Logic Circuits with Global Convergence Hiroshi NINOMIYA, Kunitaka EGAWA, Takeshi KAMIO and Hideki ASAI, IEEE 1996

[16] Advanced AI Search Techniques in Modern Digital Circuit Synthesis LECH JÓ ZWIAK Faculty of Electrical Engineering EH 9.24, Eindhoven University of Technology, Kluwer Academic PublisherS, Netherlands 2003.

Application of neural networks to efficient design of wireless and RF circuits and systems RavenderGoyal and [17] Vladimir Vereme, AMSACTA 2000

[18] Design of logic gates using spiking neural P systems with homogeneous neurons and astrocytes-like control Tao Song, Pan Zhen, M.L. Dennis Wong, Xun Wang, Elsevier 2016

Design and Implementation of Parallel Hierarchical Finite State Machines Valery Sklyarov, IouliiaSkliarova, [19] IEEE Explore 2008.